TPMS中無線接口電路的設計 通信與集成電路應用

TPMS(胎壓監測系統)作為現代汽車安全的關鍵組件,其核心功能依賴于高效、可靠的無線數據傳輸。無線接口電路的設計,直接關系到TPMS的性能、功耗和穩定性。本文將探討TPMS無線接口電路的設計要點,并分析其在通信設計及集成電路層面的應用。

一、TPMS系統與無線通信需求

TPMS通常由安裝在每個輪胎內的傳感器模塊和位于車內的接收器組成。傳感器模塊負責測量胎壓、溫度等數據,并通過無線方式將數據發送至接收器。因此,無線接口電路必須滿足以下要求:

- 低功耗:傳感器模塊由電池供電,需確保長達數年的使用壽命,電路設計需優化功耗。

- 高可靠性:車輛行駛環境復雜(如震動、溫度變化、電磁干擾),無線信號需穩定傳輸。

- 實時性:能及時檢測胎壓異常并報警。

- 小型化:傳感器需集成在有限空間內,要求電路高度集成。

二、無線接口電路的關鍵設計

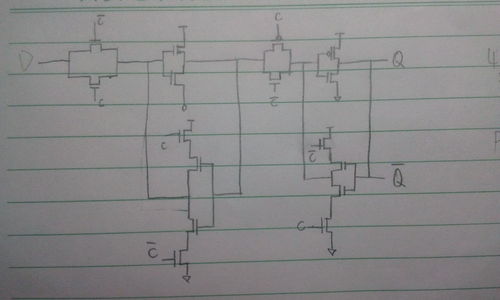

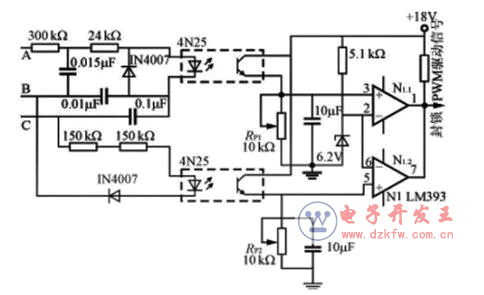

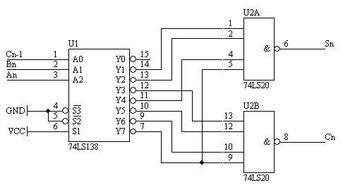

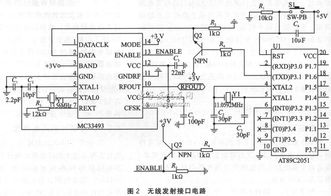

TPMS無線接口電路主要包括射頻(RF)收發模塊、天線、微控制器(MCU)及電源管理部分。

- 射頻收發芯片選擇與設計:

- 通常采用ISM頻段(如315MHz、434MHz或2.4GHz),需根據傳輸距離、功耗和法規選擇頻率。

- 集成電路設計需集成低噪聲放大器(LNA)、功率放大器(PA)、混頻器和調制解調器,以簡化外圍電路。

- 采用FSK或ASK調制方式,平衡數據速率與抗干擾能力。

- 天線設計:

- 天線需小型化(如貼片天線或螺旋天線),并匹配輪胎內的金屬環境。

- 通過仿真工具(如HFSS)優化天線增益和輻射模式,確保信號覆蓋。

- 低功耗策略:

- 電路采用休眠-喚醒模式,僅在測量和發送數據時激活射頻部分。

- 使用低功耗MCU和電源管理芯片,動態調整電壓和時鐘頻率。

- 通信協議設計:

- 設計數據幀結構,包含胎壓、溫度、傳感器ID及校驗位,以提高傳輸可靠性。

- 加入跳頻或重傳機制,應對多路徑干擾和信號碰撞。

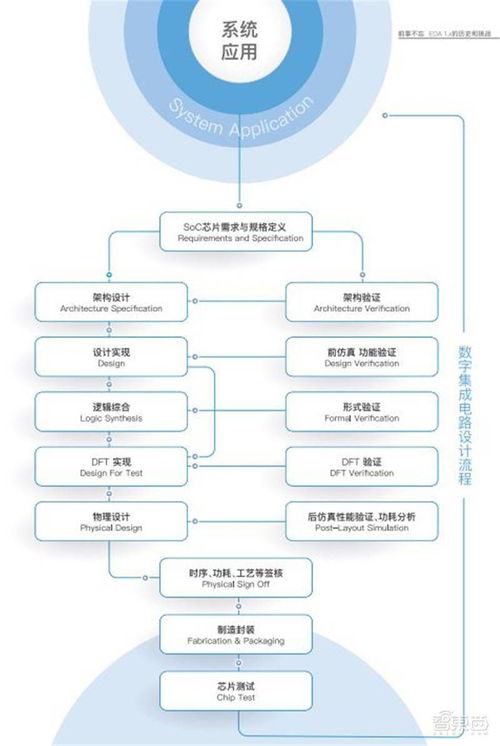

三、集成電路設計應用

隨著半導體技術的發展,TPMS無線接口電路趨向于高度集成化:

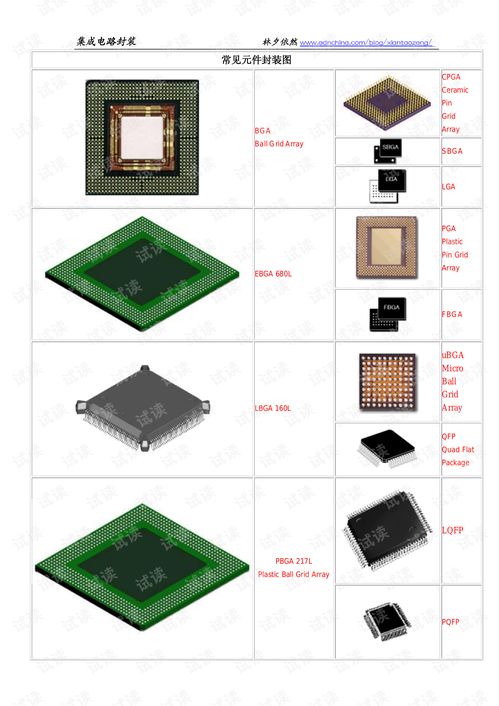

- SoC解決方案:將RF收發器、MCU、存儲器和傳感器接口集成于單芯片,減少外部元件,降低成本并提高可靠性。例如,英飛凌、恩智浦等廠商提供專用于TPMS的SoC芯片。

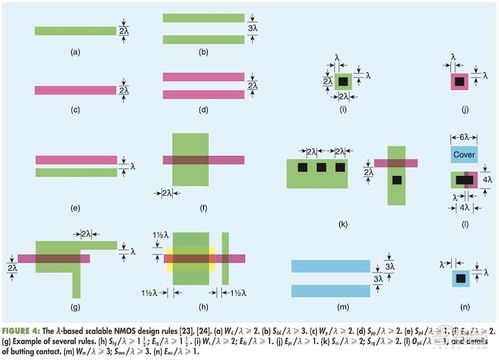

- CMOS工藝應用:采用深亞微米CMOS工藝制造RF電路,降低功耗和尺寸,同時提升集成度。

- 封裝技術:使用系統級封裝(SiP)或三維封裝,將天線、傳感器與芯片整合,適應輪胎內的苛刻環境。

- 仿真與測試:利用EDA工具(如Cadence、ADS)進行電路仿真,優化性能;并通過實車測試驗證通信距離和抗干擾能力。

四、挑戰與未來趨勢

TPMS無線接口電路設計仍面臨挑戰:電池壽命限制、多傳感器干擾(如在擁堵交通中)以及成本壓力。未來發展方向包括:

- 無源TPMS:通過能量收集技術(如振動或熱能)為電路供電,消除電池依賴。

- 智能通信:結合藍牙或UWB技術,實現與車載網絡的更高效集成。

- AI集成:在芯片中加入簡單AI算法,實現胎壓數據的智能分析與預測。

結論

TPMS無線接口電路的設計是通信技術與集成電路的融合體現。通過優化射頻性能、降低功耗并采用先進集成方案,可以提升TPMS的可靠性和實用性。隨著汽車電子化進程加速,無線接口電路將繼續向更智能、更高效的方向演進,為行車安全提供堅實保障。

如若轉載,請注明出處:http://www.xiangyujixie.cn/product/43.html

更新時間:2026-04-16 07:55:11